Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

Tags

- 자바 문제풀이

- 웹개발

- 코드스테이츠 백엔드 과정 39기

- Inverted Page Table

- 자바 알고리즘

- 문제풀이

- 다단계 페이지 테이블

- Effective Access Time

- annotation

- 프로세스 불연속 할당

- 2단계 Page Table

- Shared Page

- 알고리즘

- Page Table의 구현

- 웹 프로그래밍

- 프로세스 동기화

- 프로세스 할당

- 메모리의 불연속적 할당

- springboot

- 메모리 관리

- linux

- Segmentation with Paging

- spring

- 스프링

- 리눅스

- 운영체제

- CS

- 스프링부트

- Allocation of Physical Memory

- jpa

Archives

- Today

- Total

GrowMe

[운영체제] 메모리 관리 (5) : 다단계 Page Table 및 Paging 기타 본문

메모리 관리 (4) : 다단계 Page Table 및 Paging 기타

# Multilevel Paging and Performance

# Valid (v) / Invalid (i) Bit

# Memory Protection

# Inverted Page Table

# Shared Page

✍️ 본 포스팅은 이화여자대학교 반효경 교수님의 "운영체제" 강의를 들으며 정리한 내용입니다.

이전 포스팅에서 프로세스의 불연속적 할당에서의 Pagin 처리에서 공부해 보았다. Page Table이란 것도 배워보았는데, 이 Page Table은 2단계로도 사용할 수가 있었다. 그런데, 2단계가 아닌 다단계 Page Table로도 사용이 가능하다고 한다. 다단계 Paging을 활용한 프로세스의 불연속적 할당과 또 다른 다양한 Paging 및 Page Table에 대해 알아보자.

* Multilevel Paging and Performance

- 주소 공간이 더욱 커지면 다단계 페이지 테이블이 필요하다.

- 각 단계의 페이지 테이블이 메모리에 존재하므로 logicall address의 physical address 변환에

더 많은 메모리 접근이 필요해진다. - TLB를 통해 메모리 접근 시간을 줄일 수 있다.

- 4단계 페이지 테이블을 사용하는 경우

- 메모리 접근 시간이 100ns(4단계이므로 TLB 안쓰면 총 500ns 소요됨), TLB 접근 시간이 20ns이고

- TLB hit ratio(TLB를 통해 직접 주소 변환되는 비율)가 98%인 경우

4단계

effective memory access time = 0.98 * 120(TLB로 주소변환 20ns + 실제 데이터 접근 1회 100) + 0.02 * 520(주소 변환 100 * 4 + TLB 없는 것 확인 20 + 실제 데이터 접근 1회 100) = 128ns - 결과적으로 주소 변환을 위해 28ns만 소요된다. (생각보다 오버헤드가 되지는 않는 것을 알 수 있다.)

* 페이지 테이블 에서의 Valid (v) / Invalid (i) Bit

- 페이지 테이블에는 좌측 logical memory의 인덱스 순서에 따라 frame number가 존재한다.

- 또한 우측 physical memory에는 페이지 테이블의 frame number에 따른 인덱스에 실제 페이지가 올라가 있다.

- physical memory를 살펴보면 각 frame number에 실제 페이지가 올라가 있는 것도 있고 아닌 것도 있다.

- 페이지 테이블의 valid - invalid bit은 바로 이처럼 physical memory에 해당 페이지가 올라가 있는지를 알려준다.

- v이면 실제 올라가 있는 것이고, i이면 해당 frame number가 비어있다는 의미이다.

- 비어있는 경우는 (1)이 프로세스가 그 주소 부분을 사용하지 않거나

(2)해당 페이지가 physical memory에 올라가 있지 않고, swap area(backing store)에 존재함을 의미한다.

* Memory Protection

페이지 테이블의 각 entry는 각각 아래의 bit를 둔다.

- Protection bit

- page에 대한 접근 권한을 의미한다. (read / write / read-only)

- Valid - invalid bit

- 바로 위에서 자세히 설명하였으므로 넘어가도록 하겠다.

*Inverted Page Table

- 페이지 테이블이 매우 큰 이유

- 모든 프로세스마다 그 logical 주소에 대응하는 모든 page에 대해 페이지 테이블 엔트리가 존재한다.

- 대응하는 page가 메모리에 있든 없든 간에 페이지 테이블에는 entry로 존재하게 된다.

- Inverted page table (역방향 페이지 테이블)

- logical memory가 아니라, physical memory에 존재하는

Page frame 하나 당 페이지 테이블에 하나의 entry를 두는 것 (system-wide)

-> 실제 존재하는 것만 memory에 두기 때문에 기존보다 메모리적으로 효율적이다! - 각 페이지 테이블 엔트리는 각각의 physical memory의 page frame이 담고 있는 내용을 표시한다.

(process-id, process의 logical address) - 단점 : 테이블 전체를 탐색해야 주소변환이 가능하다.

- 대안 : associative register를 사용한다. -> 병렬적으로 동시에 검색 (비용이 비쌈)

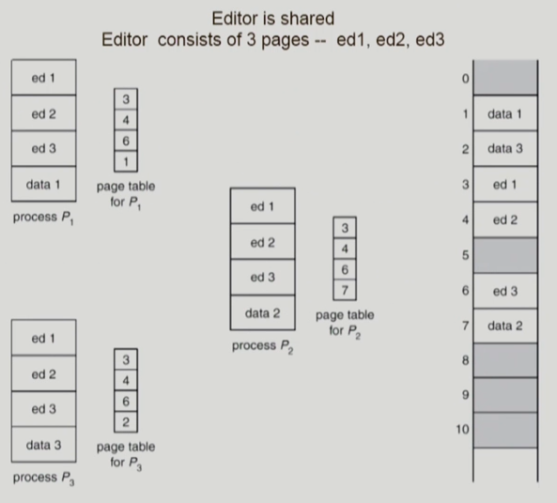

*Shared Page

- Shared code

각 프로세스마다 겹치는(중복된) 코드들은 하나의 physical 공간을 사용하도록 함.

- Re-entrant Code (=Pure code) : 재 진입 가능 코드

- read-only로 하여 프로세스 간에 하나의 code만 메모리에 올린다.

(ex : text editors, compilers, window systems) - shared code는 모든 프로세스의 logical 주소 공간에서 동일한 위치에 있어야 한다.

- 위 그림을 보면 ed1, ed2, ed3이 shared Page에 해당한다.

- Private code and data

- 각 프로세스들은 독자적으로 메모리에 올린다.

- Private data는 logical 주소 공간의 아무 곳에 와도 무방하다.

- 위 그림을 보면 data1, data2, data3에 해당한다.

우측 physical memory를 보면 모두 다른 공간을 차지하고 있다.

'CS(Computer science)' 카테고리의 다른 글

| [운영체제] 메모리 관리 (6) : Segmentation에 대하여 (0) | 2023.01.22 |

|---|---|

| [운영체제] 메모리 관리 (4) : 프로세스의 불연속적 할당에 대해 (0) | 2023.01.19 |

| [운영체제] 메모리 관리 (3) : physical memory 할당에 관하여 (0) | 2023.01.17 |

| [운영체제] 메모리 관리 (2) : 동적인 메모리 관리에 대하여 (0) | 2023.01.17 |

| [운영체제] 메모리 관리 (1) : 컴퓨터가 메모리를 관리하는 방법 (0) | 2023.01.17 |

Comments